In a nutshell: Intel's ambitious 18A node is grappling with two significant hurdles as it approaches production: yield rates languishing below 10 percent and a critical SRAM density disadvantage compared to TSMC's competing N2 process. These challenges could impede the node's deployment across Intel's next-generation CPU, AI, and custom chip portfolios.

Recent reports indicate that Intel is facing significant yield challenges with its 18A node, potentially delaying its mass production timeline. According to the South Korean newspaper Chosun, current yield rates are below 10 percent, meaning that nearly nine out of every 10 chips manufactured are defective.

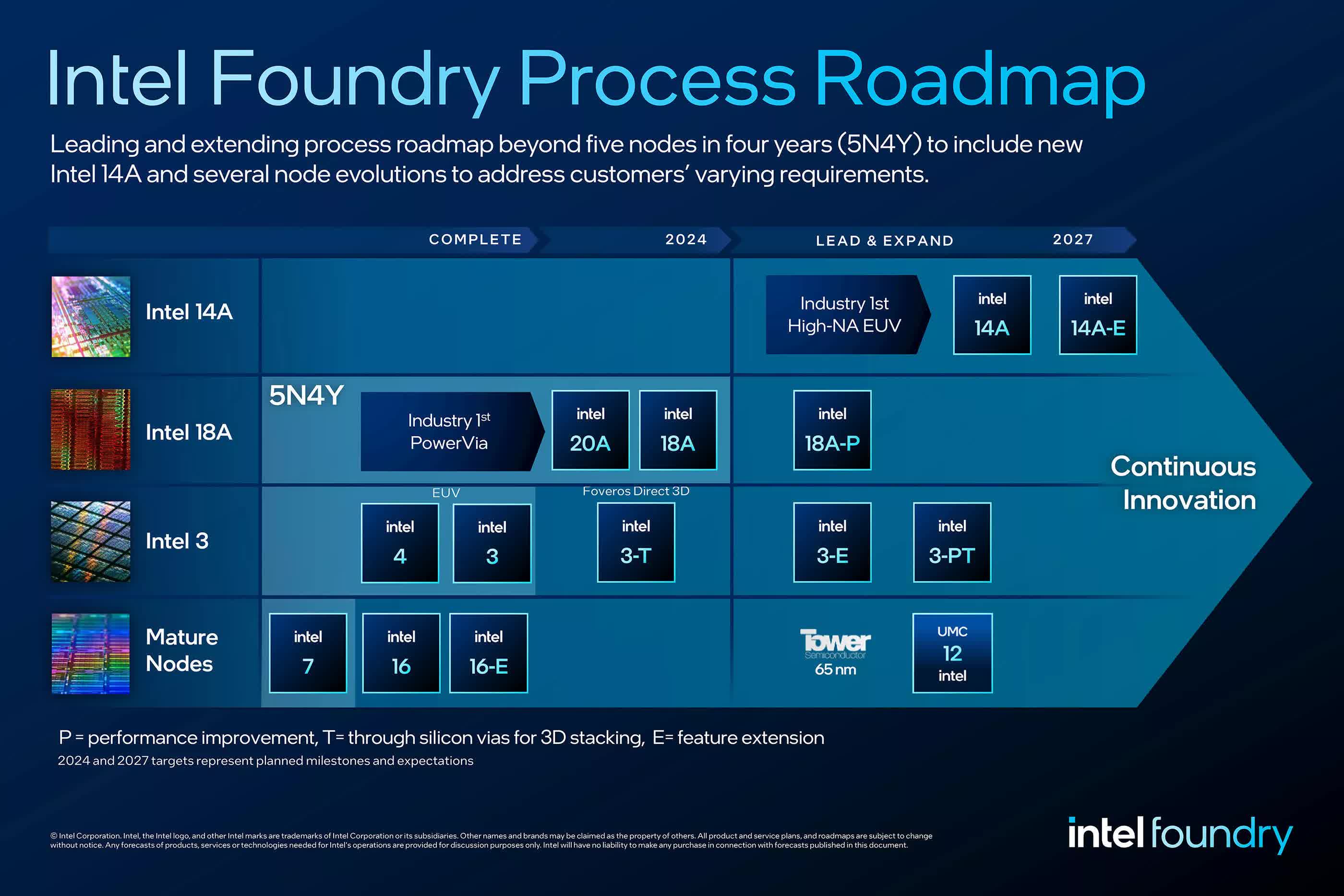

This is a major issue, particularly as Intel has already canceled its 20A (2nm class) process node for Foundry customers and shifted resources to the 18A (1.8nm class) node. If the sub-10 percent yield rate proves accurate, it could render the node unsuitable for commercial production, at least until significant improvements are made.

The challenge of packing transistors into increasingly dense layouts at these cutting-edge nodes is a formidable engineering hurdle affecting the entire semiconductor industry. Samsung's foundry yield for processes below 3nm is currently below 50 percent, with its Gate-All-Around (GAA) technology yield reportedly as low as 10 to 20 percent.

There is, however, reason for optimism regarding Intel's 18A node, as the company still has several months to refine the process ahead of its projected 2025 production ramp. The potential payoff is significant, with 18A slated to power high-profile products such as Intel's Clearwater Forest server chips, Panther Lake mobile CPUs, and custom AI silicon.

If Intel can rapidly improve 18A's yields to respectable levels – above 60 percent in the coming months – the stage could still be set for this node to drive the next generation of products from the company.

That said, yield issues aren't the only challenge Intel faces with 18A. TSMC has reportedly gained an edge in another critical area: SRAM density.

According to the ISSCC 2025 Advance Program, TSMC's N2 (2nm class) node shrinks high-density SRAM bit cells down to around 0.0175 μm², achieving a density of 38Mb/mm². In contrast, Intel's 18A node achieves 0.021 μm² and 31.8Mb/mm², which is closer to TSMC's previous-generation N3E and N5 nodes – a noticeable difference.

As chip designs demand more SRAM, increasing the density of these tiny memory cells is vital for maintaining compact, efficient designs. This is where gate-all-around (GAA) transistors come into play.

By controlling the channel on all sides, GAA transistors allow for tighter scaling compared to traditional finFETs. This tight control reduces leakage at small dimensions, enabling higher-density SRAM. Both Intel and TSMC are using GAA to shrink their SRAM bit cells, but TSMC has managed to pack them even more densely with its N2 node.

Intel 18A node reportedly stuck at 10% yields, SRAM density also trails TSMC upcoming 2nm tech